marp: true theme: default paginate: true _paginate: false header: '' footer: '' backgroundColor: white

第三讲 基于特权级的隔离与批处理

第二节 从OS角度看RISC-V

向勇 陈渝 李国良 任炬

2025年秋季

问题

- RISC-V的各特权级的特征有什么异同?

- 如何跨越特权级?

- 各特权级的特有软件功能有哪些?

提纲

1. 主流CPU比较

- RISC-V系统模式

- RISC-V系统编程:用户态编程

- RISC-V系统编程:M-Mode编程

- RISC-V系统编程:内核编程

本节主要目标

- 了解 RISC-V 特权级和硬件隔离方式

- 了解 RISC-V 的 M-Mode 和 S-Mode 的基本特征

- 了解OS在 M-Mode 和 S-Mode 下如何访问和控制计算机系统

- 了解不同软件如何在 M-Mode<–>S-Mode<–>U-Mode 之间进行切换

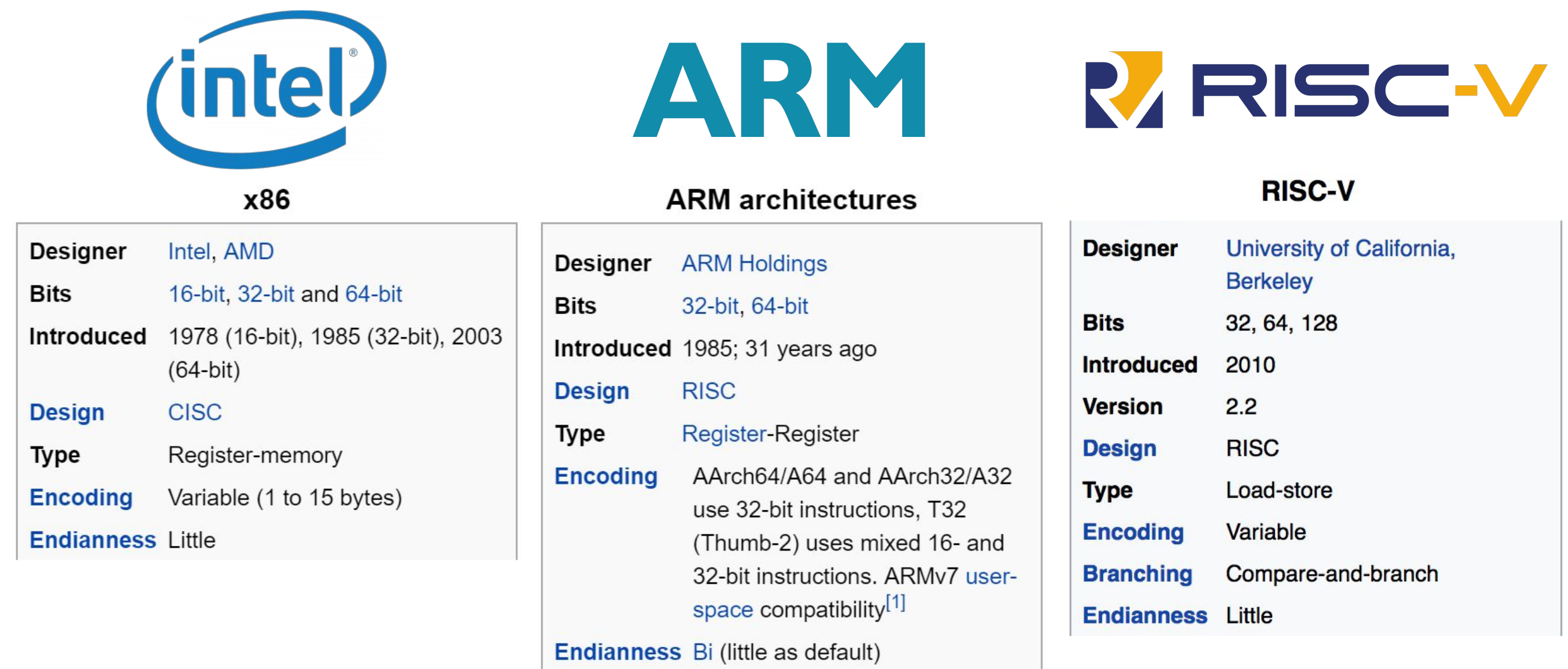

主流CPU比较

主流CPU比较

- 由于兼容性和历史原因,导致x86和ARM的设计实现复杂

- RISC-V简洁/灵活/可扩展

提纲

2.1 概述

2.2 特权级 2.3 CSR寄存器

RISC-V 系统模式

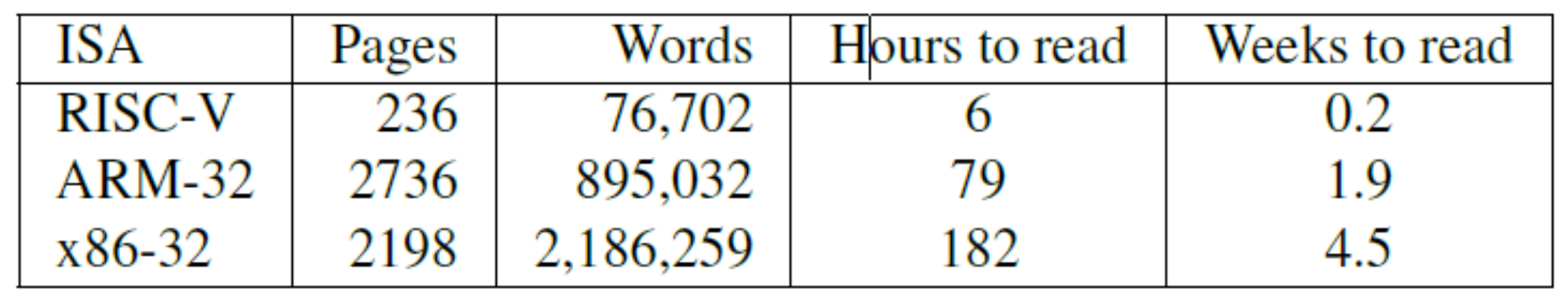

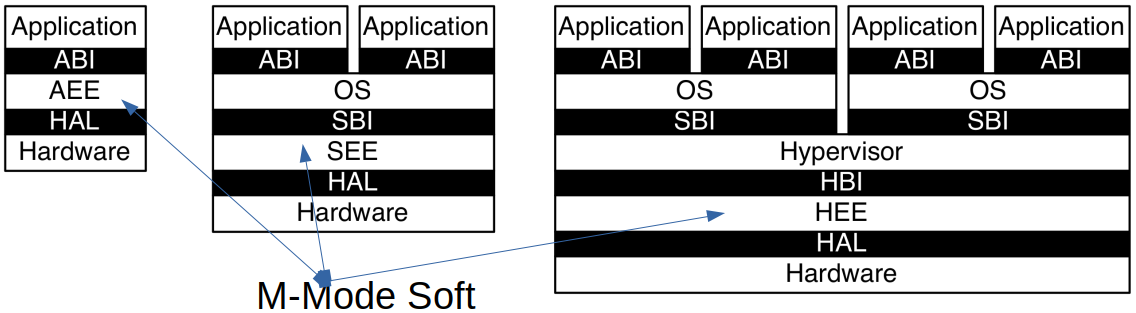

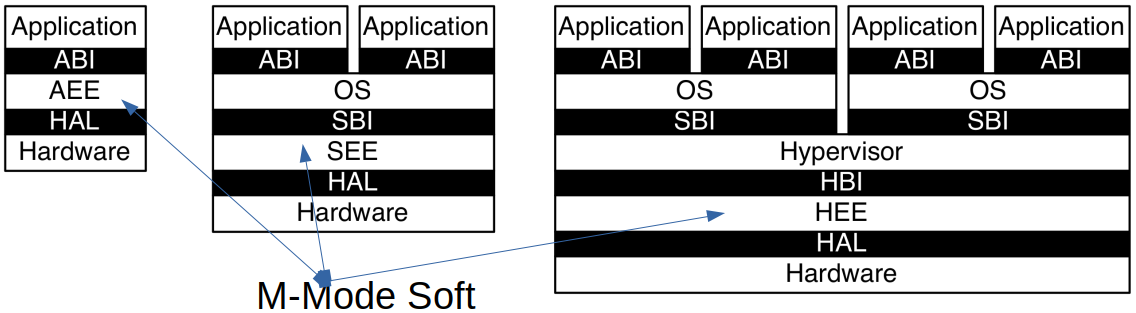

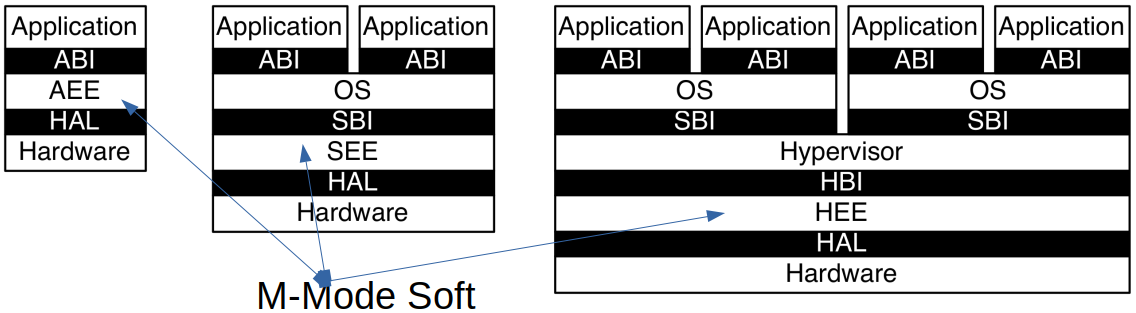

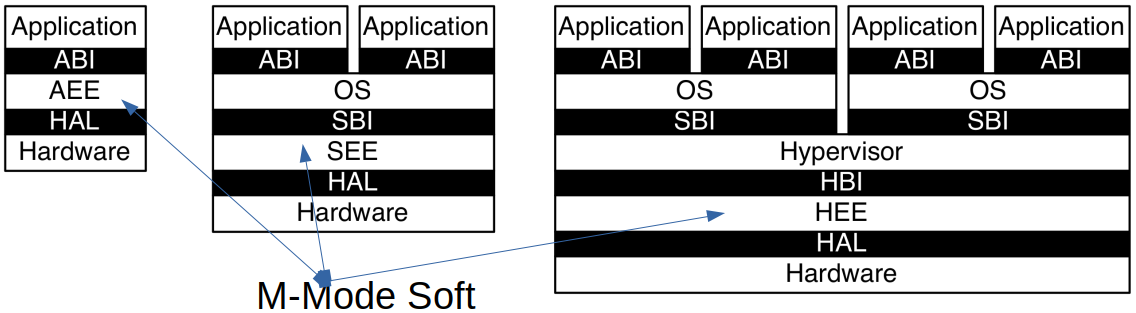

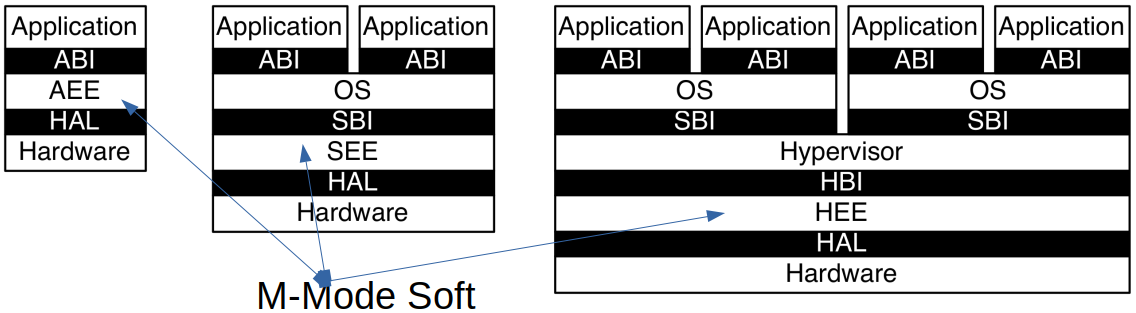

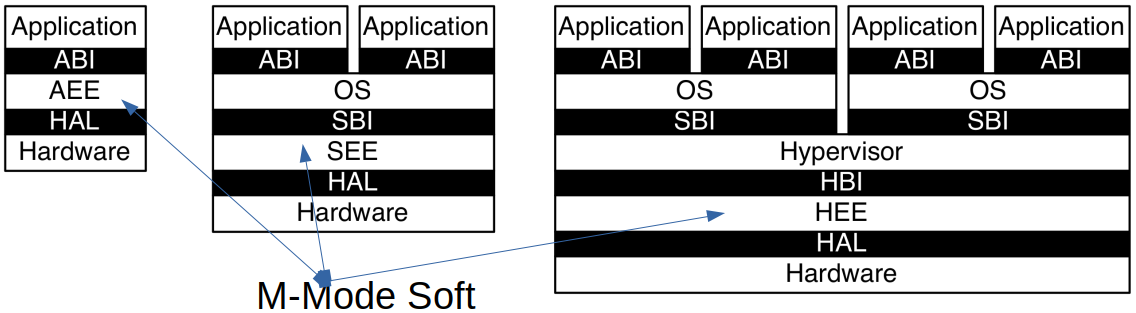

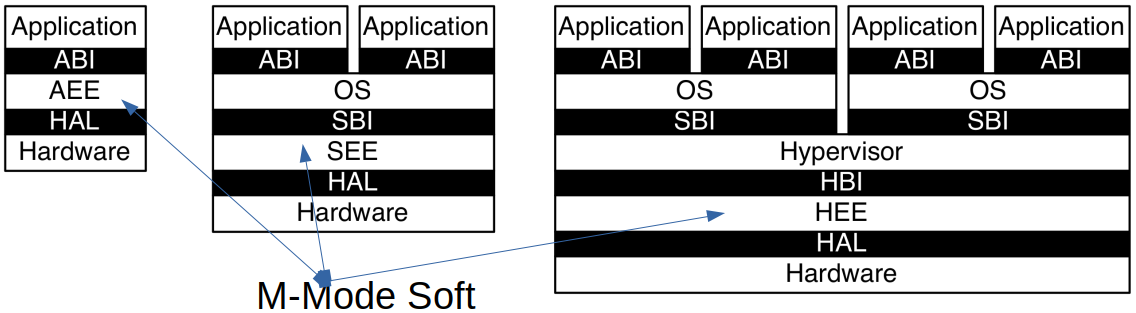

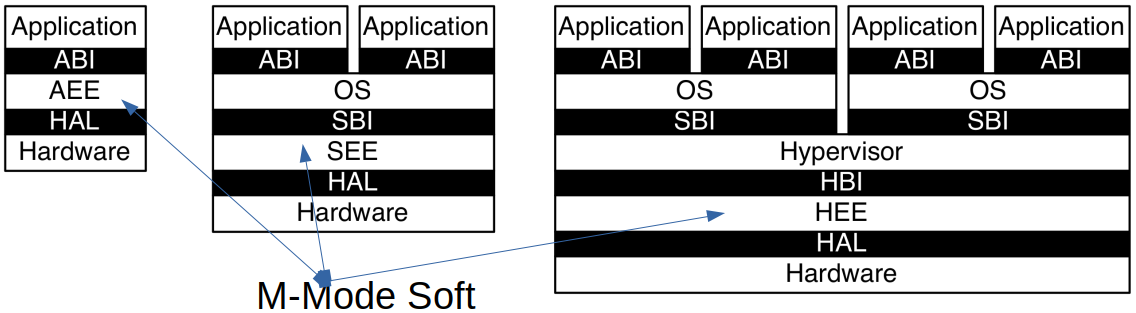

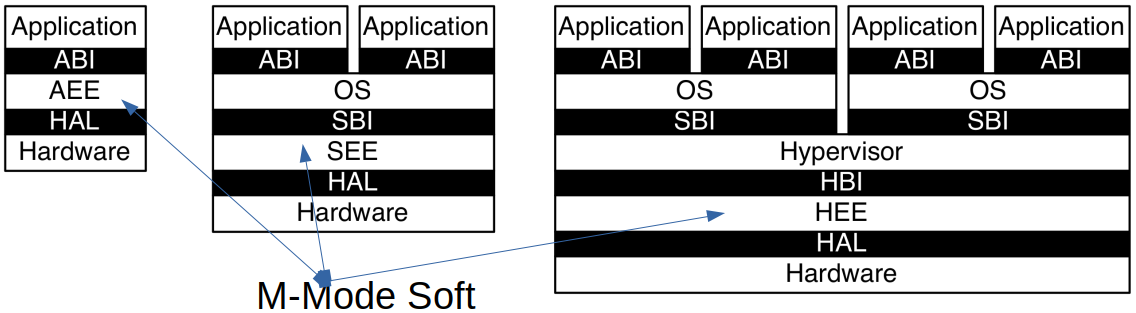

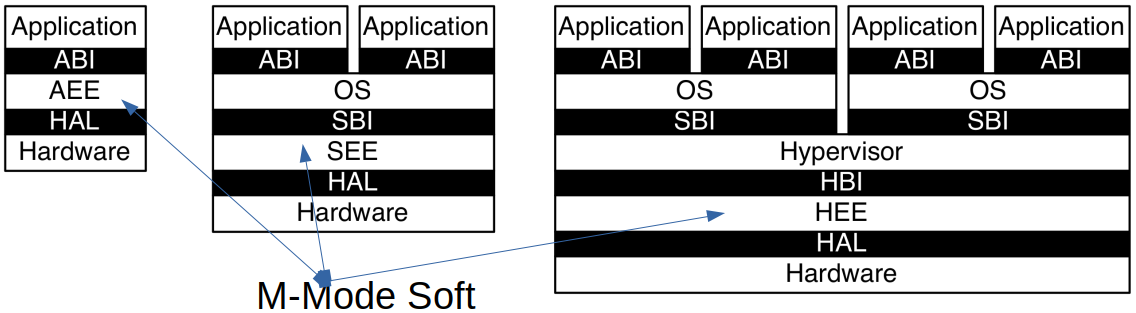

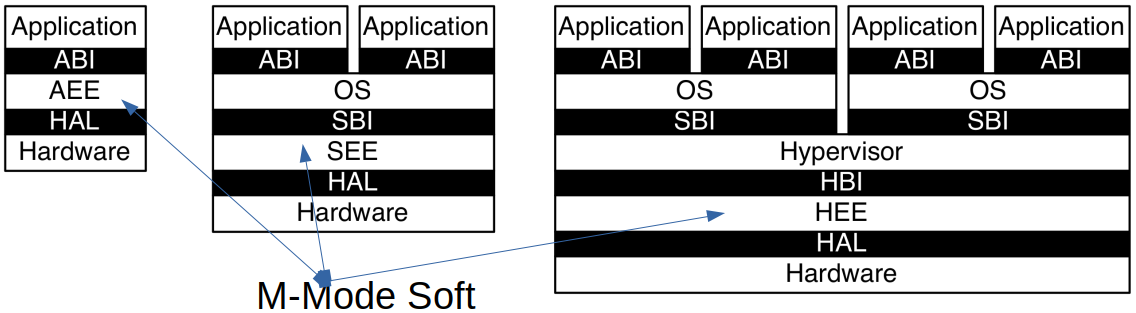

与系统编程相关的RISC-V模式

- ABI/SBI/HBI:Application/Supervisor/Hypervisor Bianry Interface

- AEE/SEE/HEE:Application/Superv/Hyperv Execution Environment

- HAL:Hardware Abstraction Layer

- Hypervisor,虚拟机监视器(virtual machine monitor,VMM)

RISC-V相关术语

- 应用执行环境 (Application Execution Environment, AEE)

- 应用程序二进制接口 (Application Binary Interface, ABI)

- 内核二进制接口 (Supervisor Binary Interface, SBI)

- 内核执行环境 (Supervisor Execution Environment, SEE)

- 虚拟机监控器二进制接口 (Hypervisor Binary interface,HBI)

- 虚拟机监控器执行环境 (Hypervisor Execution Environment, HEE)

RISC-V 系统模式:单应用场景

- 不同软件层有清晰的特权级硬件隔离支持

- 左侧的单个应用程序被编码在ABI上运行

- ABI是用户级ISA(Instruction Set Architecture)和AEE交互的接口

- ABI对应用程序隐藏了AEE的细节,使得AEE具有更大的灵活性

RISC-V 系统模式:操作系统场景

- 中间加了一个传统的操作系统,可支持多个应用程序的多道运行

- 每个应用程序通过ABI和OS进行通信

- RISC-V操作系统通过SBI和SEE进行通信

- SBI是OS内核与SEE交互的接口,支持OS的ISA

RISC-V 系统模式:虚拟机场景

- 右侧是虚拟机场景,可支持多个操作系统

RISC-V 系统模式:应用场景

- M Mode:小型设备(蓝牙耳机等)

- U+M Mode:嵌入式设备(电视遥控器、刷卡机等)

- U+S+M Mode:手机

- U+S+H+M Mode:数据中心服务器

RISC-V 系统模式:控制权接管

- 特权级是为不同的软件栈部件提供的一种保护机制

- 当处理器执行当前特权模式不允许的操作时将产生一个异常,这些异常通常会产生自陷(trap)导致下层执行环境接管控制权

提纲

- 主流CPU比较

- RISC-V系统模式

- RISC-V系统编程:用户态编程

- RISC-V系统编程:M-Mode编程

- RISC-V系统编程:内核编程

RISC-V 系统模式:多个特权级

- 现代处理器一般具有多个特权级的模式(Mode)

- U:User | S: Supervisor | H: Hypervisor | M: Machine

为何有这4种模式? 它们的区别和联系是啥?

RISC-V 系统模式:执行环境

| 执行环境 | 编码 | 含义 | 跨越特权级 |

|---|---|---|---|

| APP | 00 | User/Application | ecall |

| OS | 01 | Supervisor | ecall sret |

| VMM | 10 | Hypervisor | --- |

| BIOS | 11 | Machine | ecall mret |

- M, S, U 组合在一起的硬件系统适合运行类似UNIX的操作系统

RISC-V 系统模式:特权级的灵活组合

- 随着应用的需求变化,需要灵活和可组合的硬件构造

- 所以就出现了上述4种模式,且模式间可以组合的灵活硬件设计

RISC-V 系统模式:用户态

- U-Mode (User Mode,用户模式、用户态)

- 应用程序运行的用户态CPU执行模式

- 非特权级模式(Unprivileged Mode):基本计算

- 不能执行特权指令,不能直接影响其他应用程序执行

RISC-V 系统模式:内核态

- S-Mode(Supervisor Mode, Kernel Mode,内核态,内核模式)

- 操作系统运行的内核态CPU执行模式

- 在内核态的操作系统具有足够强大的硬件控制能力

- 特权级模式(Privileged Mode):限制APP的执行与内存访问

- 能执行内核态特权指令,能直接影响应用程序执行

RISC-V 系统模式:H-Mode

- H-Mode(Hypervisor Mode, Virtual Machine Mode,虚拟机监控器)

- 虚拟机监控器运行的Hypervisor Mode CPU执行模式

- 特权级模式:限制OS访问的内存空间的访问范围和访问方式

- 可执行H-Mode特权指令,能直接影响OS执行

RISC-V 系统模式:M-Mode

- M-Mode(Machine Mode, Physical Machine Mode)

- Bootloader/BIOS运行的Machine Mode CPU执行模式

- 特权级模式:控制物理内存,直接关机

- 能执行M-Mode特权指令,能直接影响上述其他软件的执行

提纲

- 主流CPU比较

- RISC-V系统模式

- RISC-V系统编程:用户态编程

- RISC-V系统编程:M-Mode编程

- RISC-V系统编程:内核编程

2.1 概述 2.2 特权级

2.3 CSR寄存器

RISC-V CSR寄存器分类

- 通用寄存器 x0-x31

- 一般指令访问

- 非特权指令可以使用的速度最快的存储单元

- 控制状态寄存器(CSR:Control and Status Registers)

- 通过控制状态寄存器指令访问,可以有4096个CSR

- 运行在用户态的应用程序不能访问大部分的CSR寄存器

- 运行在内核态的操作系统通过访问CSR寄存器控制计算机

通过CSR寄存器实现的隔离

OS通过硬件隔离手段(三防)来保障计算机的安全可靠

- 设置 CSR(控制状态寄存器) 实现隔离

- 控制:防止应用访问系统管控相关寄存器

- 地址空间控制寄存器:mstatus/sstatus CSR(中断及状态)

- 时间:防止应用长期使用 100%的 CPU

- 中断配置寄存器:sstatus/stvec CSR(中断跳转地址)

- 数据:防止应用破坏窃取数据

- 地址空间配置寄存器:sstatus/stvec/satp CSR (分页系统)

- 控制:防止应用访问系统管控相关寄存器

CSR寄存器功能

- 信息类:主要用于获取当前芯片id和cpu核id等信息。

- Trap设置:用于设置中断和异常相关寄存器。

- Trap处理:用于处理中断和异常相关寄存器。

- 内存保护:有效保护内存资源

Risc-V中异常和中断统称Trap

提纲

- 主流CPU比较

- RISC-V系统模式

3. RISC-V系统编程:用户态编程

- RISC-V系统编程:M-Mode编程

- RISC-V系统编程:内核编程

系统编程简述

- 系统编程需要了解处理器的特权级架构,熟悉各个特权级能够访问的寄存器资源、内存资源和外设资源

- 编写内核级代码,构造操作系统,支持应用程序执行

- 内存管理 进程调度

- 异常处理 中断处理

- 系统调用 外设控制

- 系统编程通常没有广泛用户编程库和方便的动态调试手段的支持

- 本课程的系统编程主要集中在 RISC-V 的 S-Mode 和 U-Mode,涉及部分对M-Mode的理解

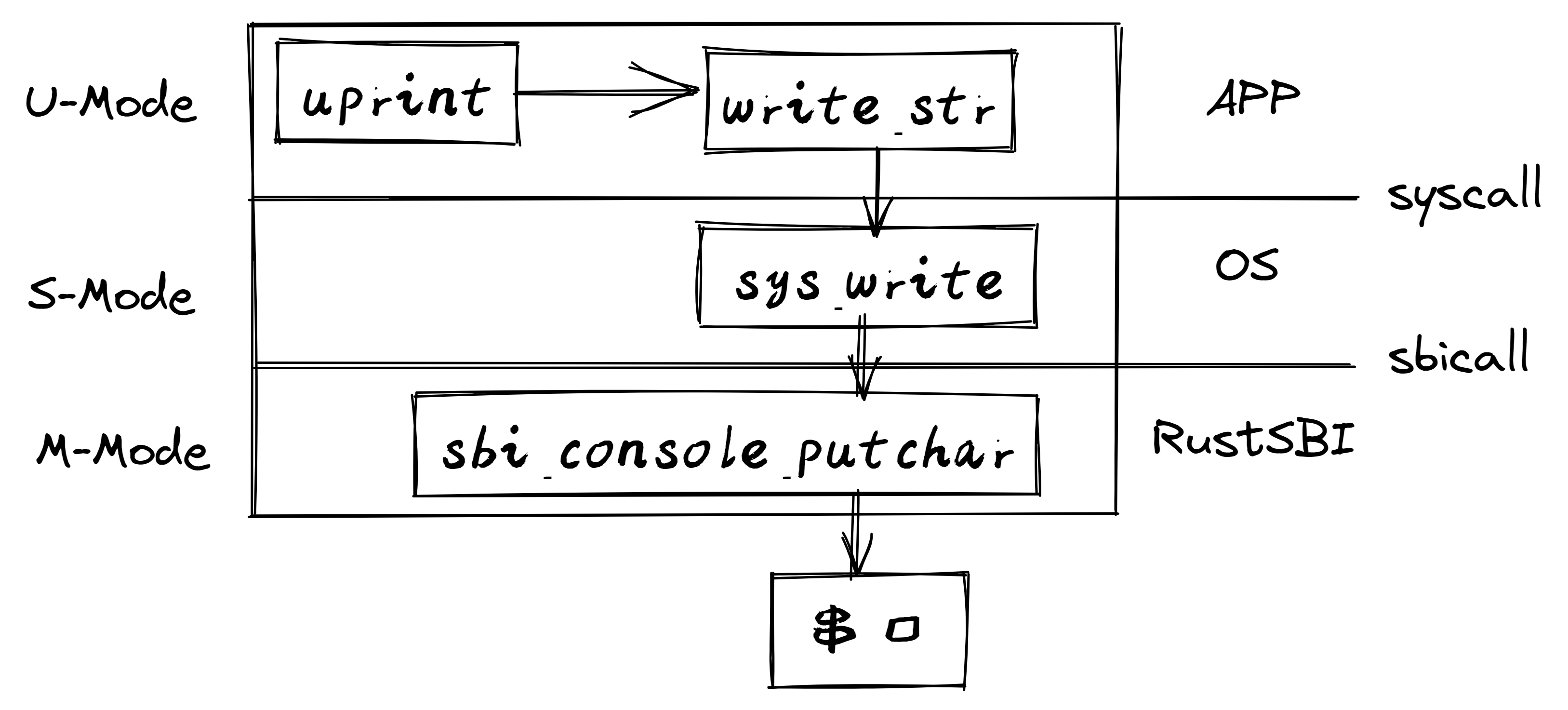

RISC-V U-Mode编程:使用系统调用

- U-Mode 下的应用程序不能够直接使用计算机的物理资源

- 环境调用异常:在执行

ecall的时候发生,相当于系统调用 - 操作系统可以直接访问物理资源

- 如果应用程序需要使用硬件资源怎么办?

- 在屏幕上打印”hello world”

- 从文件中读入数据

- 通过系统调用从操作系统中获得服务

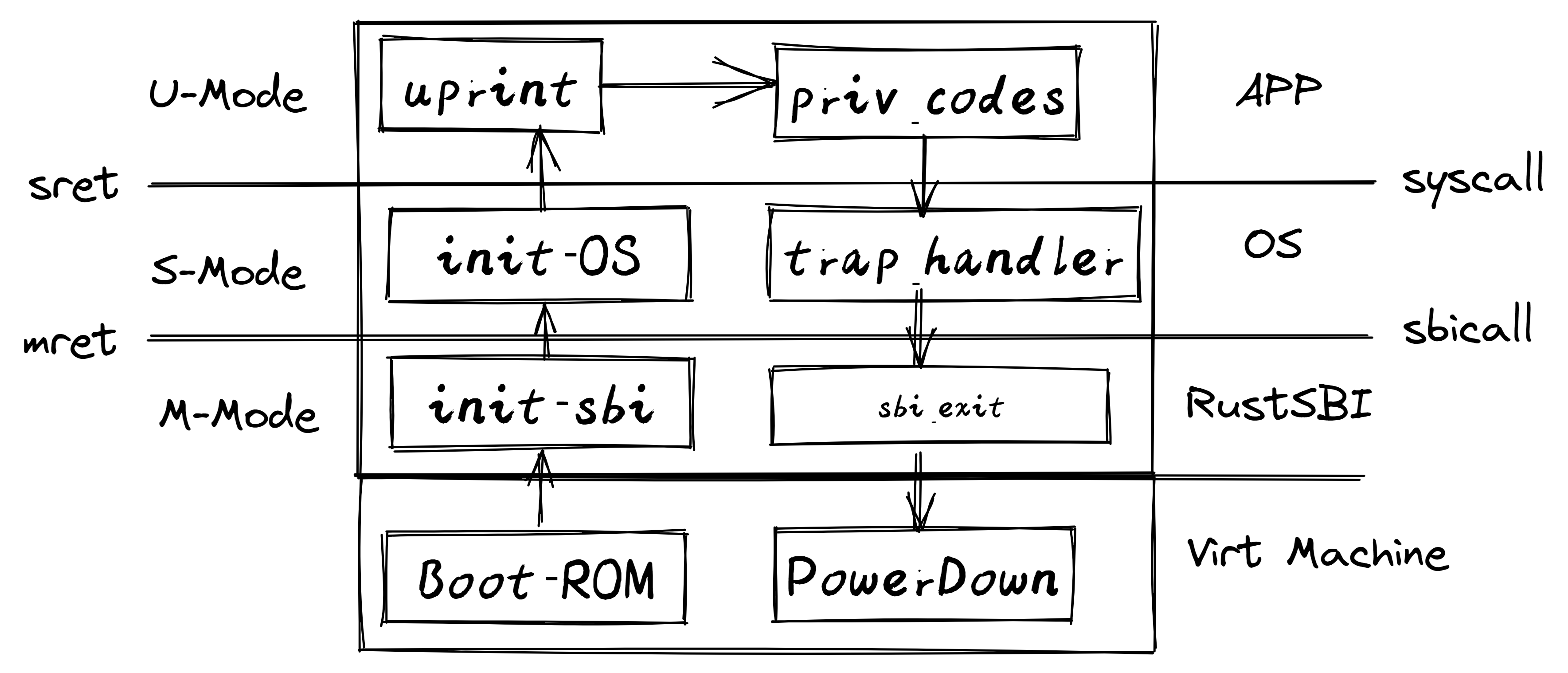

U-Mode编程:第一个例子“hello world”

在用户态打印”hello world”的小例子 大致执行流

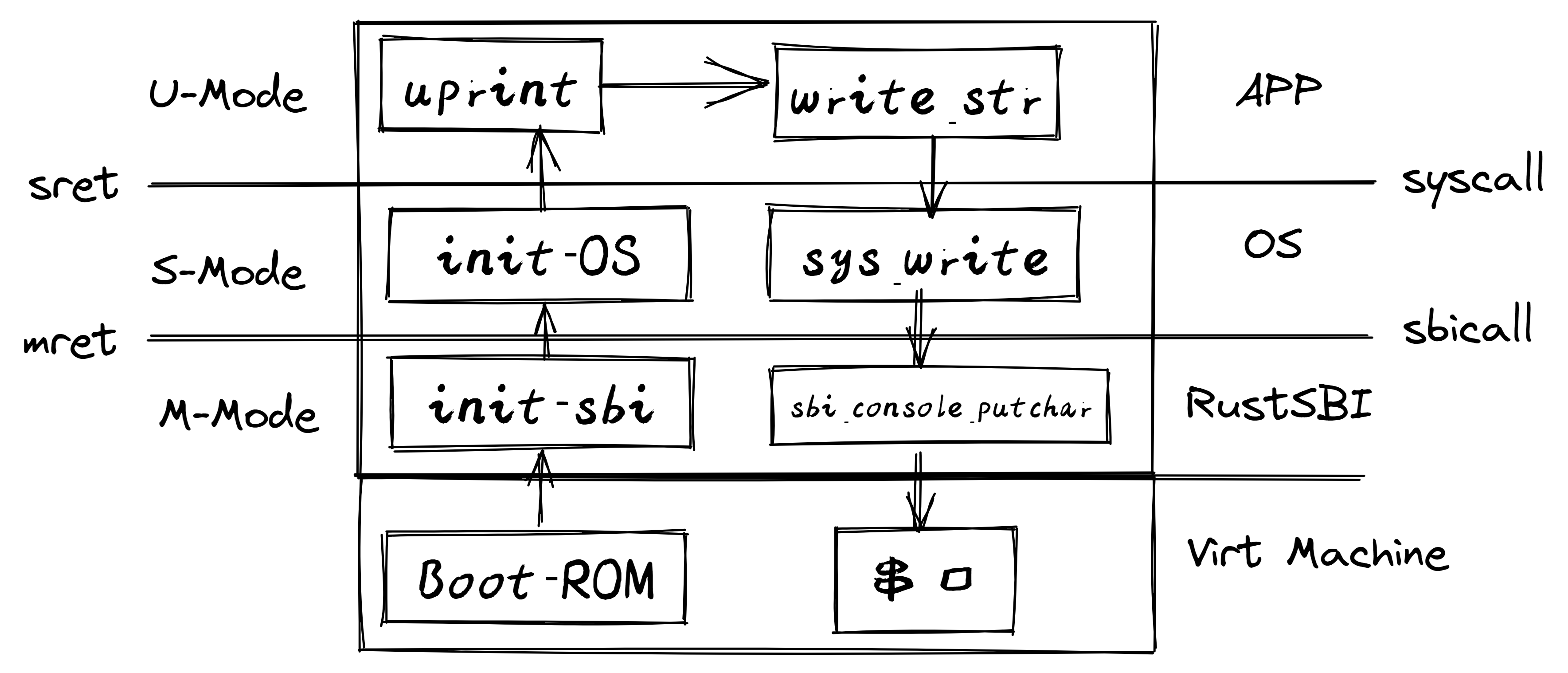

第一个例子的启动执行

在用户态打印“hello world”的小例子 启动执行流

第二个例子:在用户态执行特权指令

在用户态执行特权指令的小例子 启动与执行流程

特权操作

- 特权操作:特权指令和CSR读写操作

- 指令非常少:

mret机器模式返回sret监管者模式返回wfi等待中断 (wait for interupt)sfence.vma虚拟地址屏障(barrier)指令,用于虚拟内存无效和同步

- 很多其他的系统管理功能通过读写控制状态寄存器来实现

注:fence.i是i-cache屏障(barrier)指令,非特权指令,属于 “Zifencei”扩展规范,用于i-cache和d-cache一致性

提纲

4.1 中断机制和异常机制

4.2 中断/异常的硬件响应 4.3 中断/异常处理的控制权移交

M-Mode编程

- M-Mode是 RISC-V 中 hart(hardware thread)的最高权限模式

- M-Mode下,hart 对计算机系统的底层功能有完全的使用权

- M-Mode最重要的特性是拦截和处理中断/异常

- 同步的异常:执行期间产生,访问无效的寄存器地址,或执行无效操作码的指令

- 异步的中断:指令流异步的外部事件,中断,如时钟中断

- RISC-V 要求实现精确异常:保证异常之前的所有指令都完整执行,后续指令都没有开始执行

中断/异常的硬件响应

-

硬件

- 设置中断标记

- 依据中断向量调用相应中断服务

-

软件

- 保存当前处理状态

- 执行中断程序

- 清除中断标记

- 恢复之前的保存状态

-

中断向量表:中断--中断服务,异常--异常服务,系统调用

中断/异常开销

- 建立中断/异常/系统调用号与对应服务的开销;

- 内核堆栈的建立;

- 验证系统调用参数;

- 内核态数据拷贝到用户态;

- 内存状态改变(Cache/TLB 刷新的开销)。

M-Mode的中断控制和状态寄存器

- mtvec(MachineTrapVector)保存发生中断/异常时要跳转到的中断处理例程入口地址

- mie(Machine Interrupt Enable)中断使能寄存器

- mip(Machine Interrupt Pending)中断请求寄存器

- mstatus(Machine Status)保存全局中断以及其他的状态

- mepc(Machine Exception PC)指向发生中断/异常时的指令

- mcause(Machine Exception Cause)指示发生中断/异常的种类

- mtval(Machine Trap Value)保存陷入(trap)附加信息

- mscratch(Machine Scratch)它暂时存放一个字大小的数据

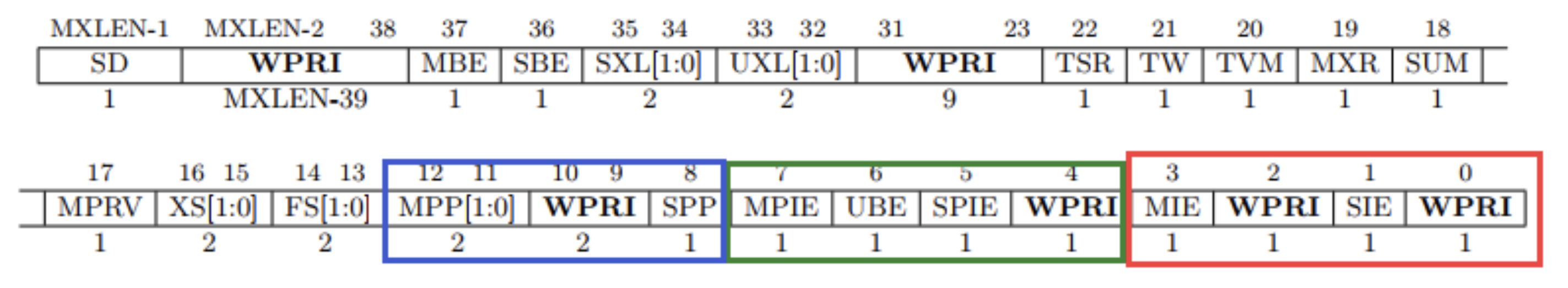

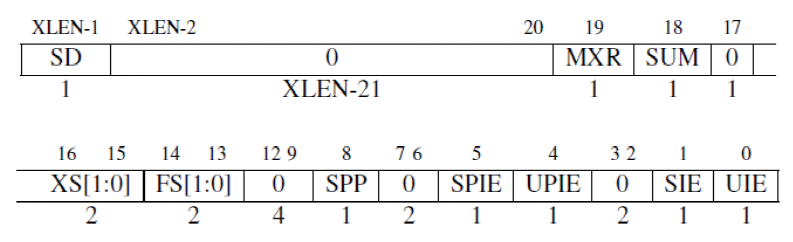

mstatus CSR寄存器

- mstatus(Machine Status)保存全局中断以及其他的状态

- SIE控制S-Mode下全局中断,MIE控制M-Mode下全局中断。

- SPIE、MPIE记录发生中断之前MIE和SIE的值。

- SPP表示变化之前的特权级别是S-Mode还是U-Mode

- MPP表示变化之前是S-Mode还是U-Mode还是M-Mode PP:Previous Privilege

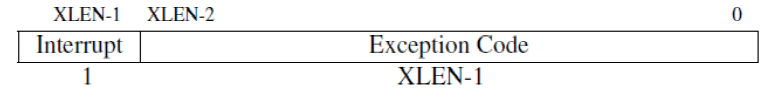

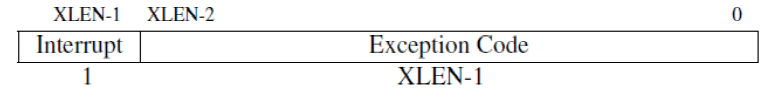

mcause CSR寄存器

当发生异常时,mcause CSR中被写入一个指示导致异常的事件的代码,如果事件由中断引起,则置上Interrupt位,Exception Code字段包含指示最后一个异常的编码。

M-Mode时钟中断Timer

- 中断是异步发生的

- 来自处理器外部的 I/O 设备的信号

- Timer 可以稳定定时地产生中断

- 防止应用程序死占着 CPU 不放, 让 OS Kernel 能得到执行权...

- 由高特权模式下的软件获得 CPU 控制权

- 高特权模式下的软件可授权低特权模式软件处理中断

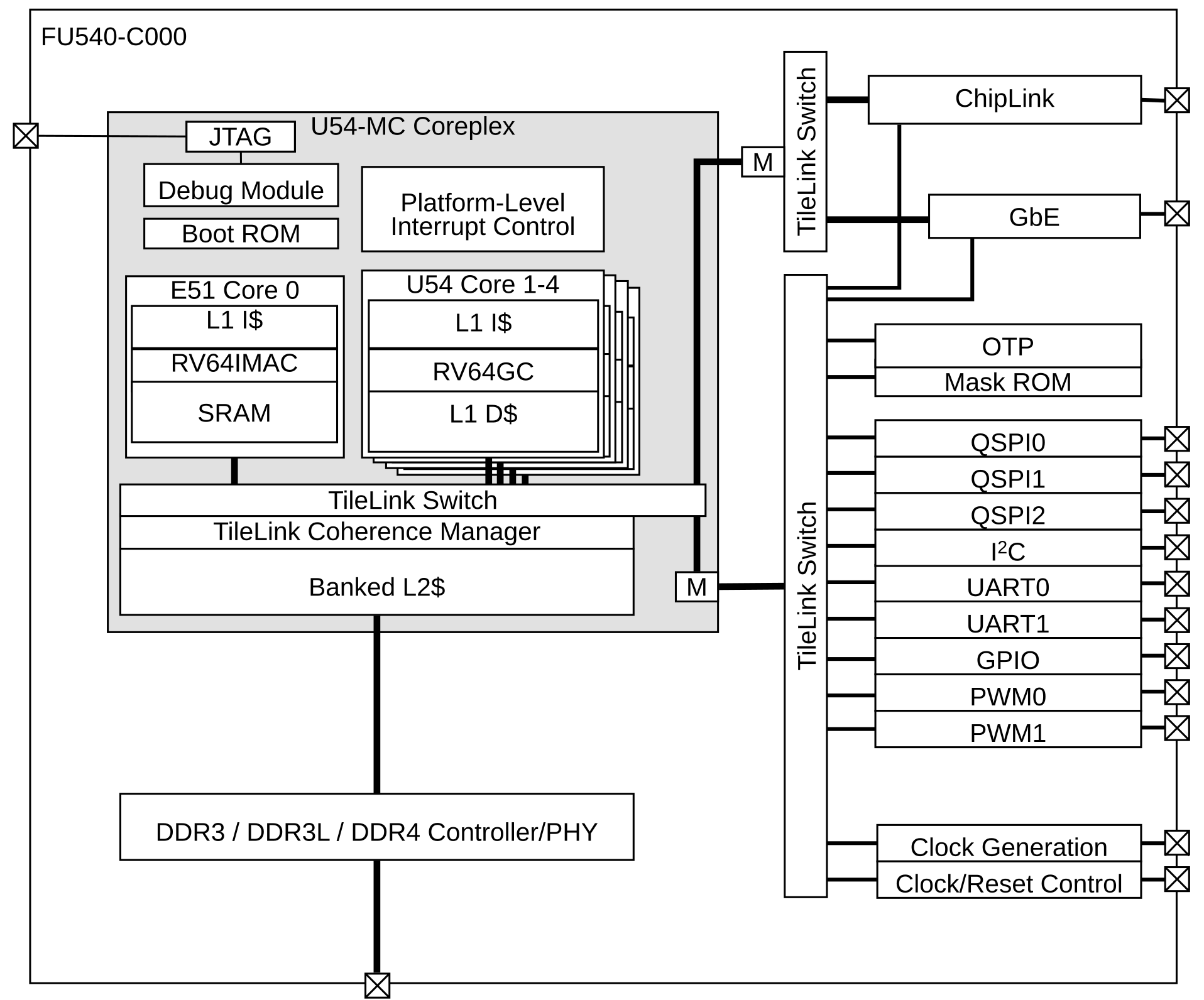

RISC-V处理器FU540模块图

提纲

- 主流CPU比较

- RISC-V系统模式

- RISC-V系统编程:用户态编程

- RISC-V系统编程:M-Mode编程

- RISC-V系统编程:内核编程

M-Mode中断的硬件响应过程

- 异常/中断指令的PC被保存在mepc中,PC设置为mtvec。

- 对于同步异常,mepc指向导致异常的指令;

- 对于中断,指向中断处理后应该恢复执行的位置。

- 根据异常/中断来源设置 mcause,并将 mtval 设置为出错的地址或者其它适用于特定异常的信息字

- 把mstatus[MIE位]置零以禁用中断,并保留先前MIE值到MPIE中

- SIE控制S模式下全局中断,MIE控制M模式下全局中断;

- SPIE记录的是SIE中断之前的值,MPIE记录的是MIE中断之前的值

- 保留发生异常之前的权限模式到mstatus 的 MPP 域中,然后更改权限模式为M。(MPP表示变化之前的特权级别是S、M or U模式)

M-Mode中断分类

通过 mcause 寄存器的不同位(mie)来获取中断的类型。

- 软件中断:通过向内存映射寄存器写入数据来触发,一个 hart 中断另外一个hart(处理器间中断)

- 时钟中断:hart 的时间计数器寄存器 mtime 大于时间比较寄存器 mtimecmp

- 外部中断:由中断控制器触发,大部分情况下的外设都会连到这个中断控制器

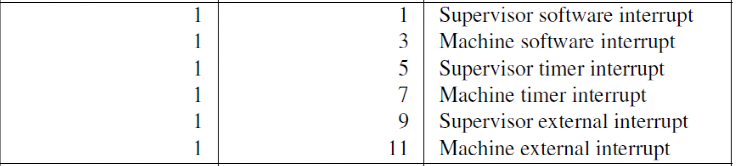

RISC-V 的中断/异常

通过 mcause 寄存器的不同位来获取中断源的信息。

第一列1代表中断,第2列代表中断ID,第3列中断含义

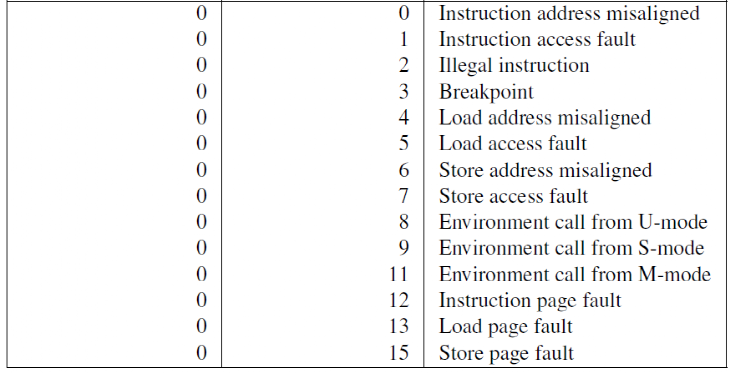

M-Mode RISC-V异常机制

通过 mcause 寄存器的不同位来获取导致异常的信息。

第一列0代表异常,第2列代表异常ID,第3列异常含义

M-Mode中断/异常的硬件响应

- 中断/异常的指令的 PC 被保存在 mepc 中, PC 被设置为 mtvec。

- 对于异常,mepc指向导致异常的指令

- 对于中断,mepc指向中断处理后应该恢复执行的位置

- 根据中断/异常来源设置 mcause(用于标识中断和异常的原因)

- 并将 mtval 设置为出错的地址或者其它适用于特定异常的信息字(提供了关于出错的具体信息)。

M-Mode中断/异常的硬件响应

- mstatus负责控制特权级别、全局中断使能和其他关键系统功能

- 把控制状态寄存器 mstatus[MIE位]置零以禁用中断,并保留先前的 MIE 值到 MPIE 中。

- SIE控制S-Mode下全局中断,MIE控制M-Mode下全局中断;

- SPIE记录SIE中断之前的值,MPIE记录MIE中断之前的值)

- 发生异常之前的权限模式保留在 mstatus 的 MPP 域中,再把权限模式更改为M

- MPP表示变化之前的特权级别是S、M or U-Mode

- 跳转到mtvec CSR设置的地址继续执行

提纲

- 主流CPU比较

- RISC-V系统模式

- RISC-V系统编程:用户态编程

- RISC-V系统编程:M-Mode编程

- RISC-V系统编程:内核编程

4.1 中断机制和异常机制 4.2 中断/异常的硬件响应

4.3 中断/异常处理的控制权移交

M-Mode中断/异常处理的控制权移交

- 默认情况下,所有的中断/异常都使得控制权移交到 M-Mode的中断/异常处理例程

- M-Mode的中断/异常处理例程可以将中断/异常重新导向 S-Mode

- 但是这些额外的操作会减慢中断/异常的处理速度

- RISC-V 提供一种中断/异常委托机制,通过该机制可以选择性地将中断/异常交给 S-Mode处理,而完全绕过 M-Mode

M-Mode中断/异常处理的控制权移交

- mideleg/medeleg (Machine Interrupt/Exception Delegation)CSR 控制将哪些中断/异常委托给 S-Mode处理

- mideleg/medeleg 中的每个位对应一个中断/异常

- 如 mideleg[5] 对应于 S-Mode的时钟中断,如果把它置位,S-Mode的时钟中断将会移交 S-Mode的中断/异常处理程序,而不是 M-Mode的中断/异常处理程序

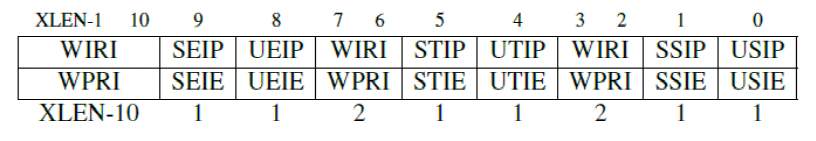

- 委托给 S-Mode的任何中断都可以被 S-Mode的软件屏蔽。sie(Supervisor Interrupt Enable) 和 sip(Supervisor Interrupt Pending)CSR 是 S-Mode的控制状态寄存器

中断委托寄存器mideleg

- mideleg (Machine Interrupt Delegation)控制将哪些中断委托给 S 模式处理

- mideleg 中的每个为对应一个中断/异常

- mideleg[1]用于控制是否将核间中断交给s模式处理

- mideleg[5]用于控制是否将定时中断交给s模式处理

- mideleg[9]用于控制是否将外部中断交给s模式处理

异常委托寄存器medeleg

- medeleg (Machine Exception Delegation)控制将哪些异常委托给 S 模式处理

- medeleg 中的每个为对应一个中断/异常

- medeleg[1]用于控制是否将指令获取错误异常交给s模式处理

- medeleg[12]用于控制是否将指令页异常交给s模式处理

- medeleg[9]用于控制是否将数据页异常交给s模式处理

中断/异常处理的控制权移交

- 发生中断/异常时,处理器控制权通常不会移交给权限更低的模式

- 例如 medeleg[15] 会把 store page fault 委托给 S-Mode

- M-Mode下发生的异常总是在 M-Mode下处理

- S-Mode下发生的异常总是在 M-Mode,或者在 S-Mode下处理

- 上述两种模式发生的异常不会由 U-Mode处理

Why?

思考题

- 如何通过断点异常来实现调试器的断点调试功能?

- 如何实现单步跟踪?

提纲

- 主流CPU比较

- RISC-V系统模式

- RISC-V系统编程:用户态编程

- RISC-V系统编程:M-Mode编程

5. RISC-V系统编程:内核编程

5.1 中断/异常机制

5.2 中断/异常的处理 5.3 虚存机制

S-Mode的中断控制和状态寄存器

- stvec(SupervisorTrapVector)保存发生中断/异常时要跳转到的地址

- sie(Supervisor Interrupt Enable)中断使能寄存器

- sip(Supervisor Interrupt Pending)中断请求寄存器

- sstatus(Supervisor Status)保存全局中断以及其他的状态

- sepc(Supervisor Exception PC)指向发生中断/异常时的指令

- scause(Supervisor Exception Cause)指示发生中断/异常的种类

- stval(Supervisor Trap Value)保存陷入(trap)附加信息

- sscratch(Supervisor Scratch)不同mode交换数据中转站

sstatus寄存器

- sstatus的SIE 和 SPIE 位分别保存了当前的和中断/异常发生之前的中断使能状态

S-Mode中断/异常机制

sie & sip 寄存器是用于保存待处理中断和中断使能情况的CSR

- sie (supervisor interrupt-enabled register)

- sip(supervisor interrupt pending)

scause寄存器

当发生异常时,CSR中被写入一个指示导致中断/异常的事件编号,记录在Exception Code字段中;如果事件由中断引起,则置Interrupt位。

scause 寄存器

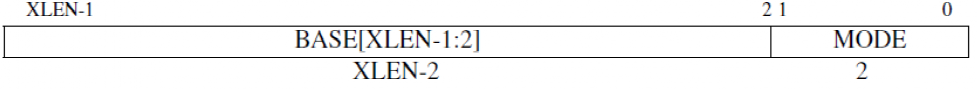

stvec 寄存器

中断/异常向量(trap-vector)基地址寄存器stvec CSR用于配置trap_handler地址

- 包括向量基址(BASE)和向量模式(MODE):BASE 域中的值按 4 字节对齐

- MODE = 0 表示一个trap_handler处理所有的中断/异常

- MODE = 1 表示每个中断/异常有一个对应的trap_handler

stvec 寄存器

提纲

- 主流CPU比较

- RISC-V系统模式

- RISC-V系统编程:用户态编程

- RISC-V系统编程:M-Mode编程

- RISC-V系统编程:内核编程

S-Mode中断/异常的硬件响应

硬件执行内容:hart 接受了中断/异常,并需要委派给 S-Mode,那么硬件会原子性的经历下面的状态转换

- 发生中断/异常的指令PC被存入 sepc, 且 PC 被设置为 stvec

- scause 设置中断/异常类型,stval被设置为出错的地址/异常相关信息

- 把 sstatus中的 SIE 位置零,屏蔽中断, SIE位之前的值被保存在 SPIE 位中

- 发生例外前的特权模式被保存在 sstatus 的 SPP(previous privilege) 域,然后设置当前特权模式为S-Mode

- 跳转到stvec CSR设置的地址继续执行

S-Mode中断/异常的软件处理

- 初始化

- 编写中断/异常的处理例程(如trap_handler)

- 设置trap_handler地址给stvec

- 软件执行

- 处理器跳转到trap_handler

- trap_handler处理中断/异常/系统调用等

- 返回到之前的指令和之前的特权级继续执行

提纲

- 主流CPU比较

- RISC-V系统模式

- RISC-V系统编程:用户态编程

- RISC-V系统编程:M-Mode编程

- RISC-V系统编程:内核编程

5.1 中断/异常机制 5.2 中断/异常的处理

5.3 虚存机制

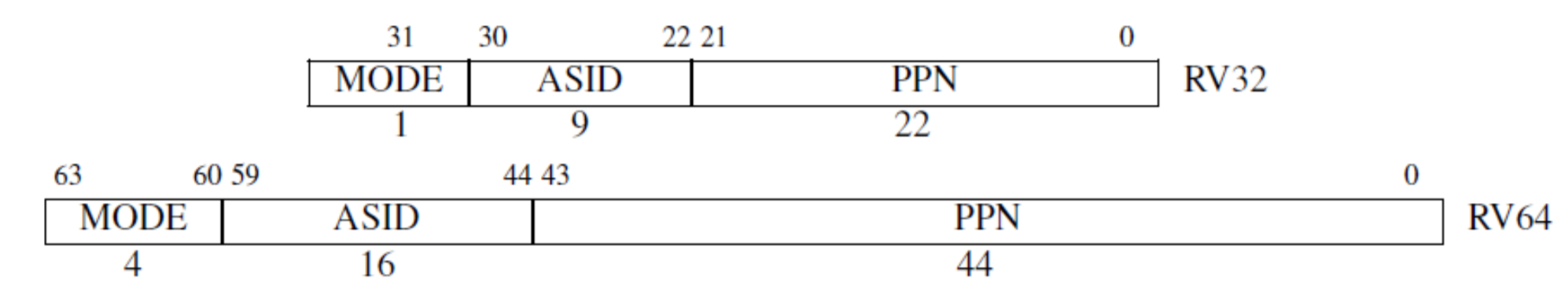

S-Mode虚拟内存系统

- 虚拟地址将内存划分为固定大小的页来进行地址转换和内容保护。

- satp(Supervisor Address Translation and Protection,监管者地址转换和保护)S模式控制状态寄存器控制分页。satp 有三个域:

- MODE 域可以开启分页并选择页表级数

- ASID(Address Space Identifier,地址空间标识符)域是可选的,避免了切换进程时将TLB刷新的问题,降低上下文切换的开销

- PPN 字段保存了根页表的物理页号

S-Mode虚存机制

RISC-V 64 支持以下 虚拟地址转换方案:

| 模式 | 虚拟地址位宽 | 页表级数 | 每级索引位数 | 物理地址位宽 |

|---|---|---|---|---|

| Sv39 | 39 位 | 3 级 | 9-9-9 | 56 位 |

| Sv48 | 48 位 | 4 级 | 9-9-9-9 | 56 位 |

| Sv57 | 57 位 | 5 级 | 9-9-9-9-9 | 56 位 |

注意:不同的模式仅影响 虚拟地址的解析,物理地址仍然受处理器实现的物理地址宽度(通常为 56 位)

S-Mode虚存机制

- 通过stap CSR建立页表基址

- 建立OS和APP的页表

- 处理内存访问异常

S-Mode虚存的地址转换

38 30 29 21 20 12 11 0

+------------+------------+------------+------------- +

| VPN[2] | VPN[1] | VPN[0] | Page Offset |

+------------+------------+------------+------------- +

9 bits 9 bits 9 bits 12 bits

- VPN[2], VPN[1], VPN[0](共 27 位):L2/1/0三级页表索引。

- Page Offset(12 位):页内偏移(4 KiB 页大小)。

- 页表项(Page Table Entry, PTE)8 bytes

S-Mode虚存的地址转换

(1) 读取 satp CSR

- satp.PPN 给出了L2页表基地址的 物理页号(Physical Page Number, PPN)。

- satp.MODE(4 bits):8(Sv39)、9(Sv48)、10(Sv57)。

L2页表基地址 = PPN × 4 KiB

S-Mode虚存的地址转换

(2) 解析 VPN(Virtual Page Number) 根据虚拟地址提取 VPN[2], VPN[1], VPN[0],并进行 3 级页表查询。 每个页表项(PTE,Page Table Entry)大小为 64-bit,其结构如下:

63 10 9 8 7 6 5 4 3 2 1 0

+---------------+-----+---+------------ +

| PPN (44 bits) | RSW | D | A | X W R V |

+---------------+-----+---+------------ +

- PPN(物理页号):映射到下一级页表或最终物理页。

- V(Valid):有效位,1 表示有效。R/W/X(读/写/执行):页权限。A/D(Access/Dirty):访问和修改位。RSW(Reserved for Software) 为软件保留

S-Mode虚存的地址转换

三级地址翻译步骤:

- VPN[2] = VA [38:30], 给出了L2页表的索引号

L2页表的页表项(L2-PTE)地址= (satp.PPN × 4 KiB) + (VPN[2] × 8)

L2-PTE.PPN = L1页表基址的物理页号

63 10 9 8 7 6 5 4 3 2 1 0

+---------------+-----+---+------------ +

| PPN (44 bits) | RSW | D | A | X W R V |

+---------------+-----+---+------------ +

S-Mode虚存的地址转换

三级地址翻译步骤: 2. VPN[1] = VA [29:21], 给出了L1页表的索引号

L1页表的页表项(L1-PTE)地址= (L2-PTE.PPN × 4 KiB) + (VPN[1] × 8)

L1-PTE.PPN = L0页表基址的物理页号

63 10 9 8 7 6 5 4 3 2 1 0

+---------------+-----+---+------------ +

| PPN (44 bits) | RSW | D | A | X W R V |

+---------------+-----+---+------------ +

S-Mode虚存的地址转换

三级地址翻译步骤: 3. VPN[0] = VA [20:12], 给出了L0页表的索引号

L0页表的页表项(L0-PTE)地址= (L1-PTE.PPN × 4 KiB) + (VPN[0] × 8)

L0-PTE.PPN = 最终物理地址的物理页号

63 10 9 8 7 6 5 4 3 2 1 0

+---------------+-----+---+------------ +

| PPN (44 bits) | RSW | D | A | X W R V |

+---------------+-----+---+------------ +

S-Mode虚存的地址转换

- 计算物理地址

虚地址对应的最终物理地址 = (L0 PTE.PPN × 4 KiB) + Page Offset

假设: satp.PPN = 0x12345, 即L2页表基地址 = 0x12345 × 4 KiB = 0x12345000。 虚拟地址: 0x0987654321 000 1001 1000 0111 0110 1001 0100 0011 0010 0001 000100110 000111011 010010100 0011 0010 0001 VPN[2]=0x026(9 bits) VPN[1]=0x03B(9 bits) VPN[0]=0x094(9 bits) Page Offset = 0x321

S-Mode虚存的地址转换

- 计算物理地址

- VPN[2]=0x026 VPN[1]=0x03B VPN[0]=0x094

- 经过三级页表查询:

- L2中0x026号PTE 指向 L1 页表(PPN = 0x20000,L1基址)

- L1中0x03B号PTE 指向 L0 页表(PPN = 0x30000,L0基址)

- L0中0x094号PTE 指向物理页(PPN = 0x40000)

- 最终 物理地址计算:

物理地址 = (0x40000 × 4 KiB) + 0x321

= 0x40000000 + 0x321

= 0x40000321

小结

- RISC-V 特权级

- M-Mode, (H-Mode) S-Mode, U-Mode

- RISC-V 的 M-Mode 和 S-Mode 的基本特征

- 中断使能、委托和配置;页表使能和配置

- 不同软件如何在 M-Mode<–>S-Mode<–>U-Mode 之间进行切换

- ecall, mret, sret

- 中断响应过程

- 虚实地址转换过程

- 手工计算地址转换